深度解析 ATVOSS:面向 NPU 的 TVM 编译后端与张量优化系统

在异构计算的编译链路中,ATVOSS 扮演着“硬件特性注入者”的角色。它位于 TVM 编译栈的后端,负责承接前端(Relay)优化后的中间表示,并将其 Lowering(下降)为符合 CANN 架构标准的高性能算子代码。ATVOSS 的核心价值在于弥合了通用 Tensor IR 与专用 NPU 硬件架构之间的语义鸿沟。

在异构计算的编译链路中,ATVOSS 扮演着“硬件特性注入者”的角色。它位于 TVM 编译栈的后端,负责承接前端(Relay)优化后的中间表示,并将其 Lowering(下降)为符合 CANN 架构标准的高性能算子代码。ATVOSS 的核心价值在于弥合了通用 Tensor IR 与专用 NPU 硬件架构之间的语义鸿沟。

核心资源链接:

- CANN 组织链接: https://atomgit.com/cann

- ATVOSS 仓库链接: https://atomgit.com/cann/atvoss

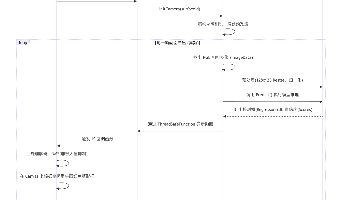

一、 编译栈中的架构定位与 IR 下降流程

ATVOSS 并不是一个独立的编译器,而是嵌入在 TVM 框架中的 NPU 专用后端(Backend)。它深度参与了从计算逻辑定义到最终代码生成的全过程。

1.1 从 TE 到 TIR 的转换

在 TVM 的架构中,用户定义的计算逻辑首先被表示为 Tensor Expression (TE)。ATVOSS 在这一层并不改变“计算什么(What to compute)”,而是开始介入“如何计算(How to compute)”。

- 硬件指令映射: ATVOSS 识别 TE 中的数学原语(如矩阵乘、卷积),并将其映射到 NPU 特有的指令集(如

mma矩阵乘指令)上。 - IR 转换: 它将高层的 DAG(有向无环图)转换为更底层的 TIR(Tensor Intermediate Representation),在这个过程中引入了循环变量、指针算术和存储访问的显式描述。

1.2 编译 Pass 的定制化

ATVOSS 注入了一系列定制化的 Optimization Pass:

- Inject Double Buffer: 自动检测数据依赖,插入双缓冲指令,以掩盖数据搬运延迟。

- Vectorization: 将标量循环转换为向量指令,适配 NPU 的 Vector Unit(向量计算单元)。

- Storage Rewrite: 重写存储访问模式,以符合 NPU 对内存对齐(Alignment)和数据排布(Format)的严格要求。

二、 硬件感知的 Tensor Schedule 定制化策略

Schedule(调度)是 TVM 优化的灵魂。ATVOSS 提供了一套针对 NPU 硬件特性的 Schedule 原语(Primitives),允许编译器精确控制计算的执行顺序。

2.1 维度变换与硬件亲和性

NPU 的 Cube Unit 通常对输入数据的形状有特定的偏好(例如 16x16 的分块)。ATVOSS 的调度策略必须包含:

- Split & Reorder(拆分与重排): 将大的张量维度拆分为

Outer和Inner循环。例如,将一个[1024, 1024]的矩阵乘法拆分为无数个[16, 16]的小块,确保最内层循环直接映射到硬件的矩阵乘指令。 - Fuse(融合): 将连续的轻量级操作(如

Element-wise Add)融合到同一个计算内核中,减少内核启动开销。

2.2 调度原语的硬件语义

ATVOSS 扩展了 TVM 的原生调度原语:

bind_task:将某个维度的循环绑定到 NPU 的多核并行任务(Block Dim)上。set_scope:显式指定某个张量存储在 Unified Buffer (UB)、L1 还是 Global Memory (GM) 中。

三、 并行计算维度的映射与流水线编排

NPU 拥有强大的并行计算能力,包括 AI Core 间的数据并行和 AI Core 内部的指令流水线并行。ATVOSS 负责将软件层面的并行度映射到物理硬件上。

3.1 多核并行(Multi-Core Parallelism)

ATVOSS 通过分析计算图的数据依赖,确定哪些维度的计算是相互独立的。

它将外层循环(Outer Loop)映射为 Block ID,使得不同的数据块被分发到不同的 AI Core 上同时执行。对于 NPU 这种众核架构,合理的负载均衡是性能的关键。

3.2 指令流水线(Instruction Pipelining)

在单个核心内部,ATVOSS 致力于实现计算与访存的重叠(Overlap)。

- DMA 与计算分离: 生成代码时,ATVOSS 会分离数据搬运指令(MTE)和计算指令(Vector/Cube)。

- 同步屏障优化: 智能插入

pipe_barrier或wait_event,确保数据在计算前已就绪,同时尽量减少 CPU/NPU 的空转等待时间。

四、 多级存储层次的显式管理与 Tiling 算法

与通用 CPU 的 Cache 自动管理不同,NPU 的高速缓存(如 Unified Buffer, L1)往往需要软件显式管理。这是 ATVOSS 区别于 GCC/LLVM 的最大特征。

4.1 内存作用域(Memory Scope)的精确控制

ATVOSS 引入了特定于 NPU 的存储作用域概念。在生成 TIR 时,它会明确标记每个 Buffer 的驻留位置:

- Global: 对应片外高带宽内存(HBM/DDR),容量大但访问慢。

- Local.L1: 对应片上 L1 缓冲区,用于 Cube 单元的输入数据暂存。

- Local.UB: 对应 Unified Buffer,用于向量运算和最终结果的累加。

4.2 基于约束的 Tiling 搜索

为了适配有限的片上内存,ATVOSS 必须对大张量进行切片(Tiling)。

它内置了一个基于约束规划(Constraint Programming)或机器学习(AutoTVM)的搜索引擎,寻找最优的 Tile Size。

- 约束条件:

Tile_Size * Data_Type_Size <= UB_Capacity。 - 目标函数: 最小化 Global Memory 的访问次数,最大化数据的复用率(Data Reuse)。

以下是一段 Python 代码示例,展示了在 TVM 中如何使用 ATVOSS 风格的调度原语来定义一个针对 NPU 优化的矩阵乘法调度:

import tvm

from tvm import te

def schedule_matmul_npu(N, M, K):

# 1. 定义计算逻辑 (Tensor Expression)

k = te.reduce_axis((0, K), "k")

A = te.placeholder((N, K), name="A")

B = te.placeholder((K, M), name="B")

# 简单的矩阵乘法定义

C = te.compute(

(N, M),

lambda i, j: te.sum(A[i, k] * B[k, j], axis=k),

name="C"

)

# 2. 创建调度对象

s = te.create_schedule(C.op)

# 3. 显式内存管理:利用 Cache Read 将数据加载到 NPU 的 Unified Buffer

AA = s.cache_read(A, "local.UB", [C])

BB = s.cache_read(B, "local.UB", [C])

CC = s.cache_write(C, "local.UB")

# 4. Tiling 策略:适配 NPU Cube Unit 的 16x16 分块要求

# 假设 block_factor=16 是硬件特定的最优粒度

block_factor = 16

# 对输出 C 的轴进行拆分 (Outer用于多核并行, Inner用于Cube指令)

i, j = C.op.axis

io, ii = s[C].split(i, factor=block_factor)

jo, ji = s[C].split(j, factor=block_factor)

# 5. 绑定 Block 维度到 AI Core (Pipeline 并行)

# 这里将外层循环映射到 TVM 的 blockIdx,对应 NPU 的多核启动

s[C].bind(io, tvm.thread_axis("blockIdx.x"))

# 6. 指令发射 (Tensorization)

# 实际场景中,这里会调用特定的 intrinsic 将最内层循环替换为 NPU 的 mma 指令

# s[CC].tensorize(ii, mma_intrinsic)

return s, [A, B, C]

五、 自动化算子融合与 Pass 优化注入

为了达到极致性能,ATVOSS 必须减少 Kernel 的启动次数和显存的读写带宽。算子融合(Operator Fusion)是实现这一目标的核心手段。

5.1 融合模式匹配

ATVOSS 利用 TVM 的 Relay 层进行图级优化。它能够识别复杂的子图模式,例如 Conv2D + BiasAdd + ReLU + Cast。

一旦匹配成功,ATVOSS 会生成一个复合函数(Composite Function),并为其生成一个融合后的 Schedule。这意味着数据在 UB 中完成卷积、加偏置、激活和类型转换等一系列操作后,才会被写回 Global Memory。

5.2 算子属性的一致性保障

在融合过程中,ATVOSS 严格遵循标准算子定义(ops-nn)的规范。

- 精度对齐: 确保融合后的中间计算精度(如 FP16 或 FP32)与分离执行时一致。

- 异常处理: 在融合算子中自动插入溢出检测逻辑,确保在数值不稳定时能够正确报错。

六、 代码生成(Codegen)与运行时回退机制

编译的最后一步是将优化后的 IR 转换为机器码或 C 源代码。ATVOSS 提供了针对 NPU 的专用 Codegen 模块。

6.1 生成 CCE/Ascend C 代码

ATVOSS 的后端并不直接生成二进制机器码,而是生成高层次的 CCE(Cube-Based Computing Engine)代码或 Ascend C 代码。

这种设计允许利用厂商提供的底层编译器(如 ccec)进行二次优化,确保寄存器分配和指令调度的微观性能。

6.2 动态 Shape 的回退(Fallback)

尽管 ATVOSS 致力于静态编译优化,但面对完全未知的动态 Shape,它具备回退机制。

- 通用内核调用: 当无法生成特定的 Tiling 参数时,ATVOSS 可以生成调用通用算子库(Generic Kernel)的代码。

- 即时编译(JIT): 在某些配置下,允许 Runtime 在执行时根据实际 Shape 触发轻量级的 JIT 编译,动态生成最优代码。

昇腾计算产业是基于昇腾系列(HUAWEI Ascend)处理器和基础软件构建的全栈 AI计算基础设施、行业应用及服务,https://devpress.csdn.net/organization/setting/general/146749包括昇腾系列处理器、系列硬件、CANN、AI计算框架、应用使能、开发工具链、管理运维工具、行业应用及服务等全产业链

更多推荐

已为社区贡献17条内容

已为社区贡献17条内容

所有评论(0)