MlaProlog算子全景透视-结构流程与依赖关系深度分析

本文系统介绍了昇腾AI处理器上MlaProlog算子的技术架构与开发实践。从硬件特性分析入手,详细阐述了基于达芬奇架构的融合算子设计原理,通过计算图优化实现3-5倍性能提升。重点讲解了从Python DSL到AscendC代码的自动编译路径,结合TVM/MLIR技术栈和多面体模型优化方法。文章还分享了企业级应用案例、性能调优技巧和故障排查指南,并展望了AI编译技术向智能生成和异构统一的发展趋势。为

目录

🚀 摘要

本文深入剖析昇腾AI处理器上MlaProlog算子的完整技术栈,从底层Ascend NPU达芬奇架构的硬件特性出发,解构融合算子的编程范式演进。通过分析MlaProlog算子的计算图结构、数据流依赖关系和流水线调度机制,揭示其相比传统算子拼接实现3-5倍性能提升的本质原因。重点探讨基于Python DSL的高层算子描述方法,结合TVM/MLIR编译技术栈,展示从计算图描述到高性能Ascend C代码的自动生成路径。文章关联CANN AKG项目的技术思路,为下一代AI算子开发提供前瞻性方法论,助力开发者实现从"手工优化"到"智能生成"的范式跃迁。

1 🎯 引言:大模型时代的算子革命

在千亿参数大模型成为AI领域标配的今天,传统算子开发模式正面临前所未有的挑战。以GPT-3 175B参数模型为例,其推理过程中单个Transformer层包含超过20个基础算子,若采用传统分离式实现,仅内核启动开销就占总计算时间的15-20%。更严重的是,中间结果在全局内存中的反复读写,导致有效计算带宽利用率不足40%。

MlaProlog算子正是在这样的背景下应运而生。它并非简单的算子组合,而是基于昇腾达芬奇架构硬件特性重新设计的计算图级融合算子。在我13年的异构计算开发生涯中,见证了从CUDA到OpenCL再到领域特定语言的演进,而MlaProlog代表的是AI计算从"通用编程"到"架构感知"的深刻转变。

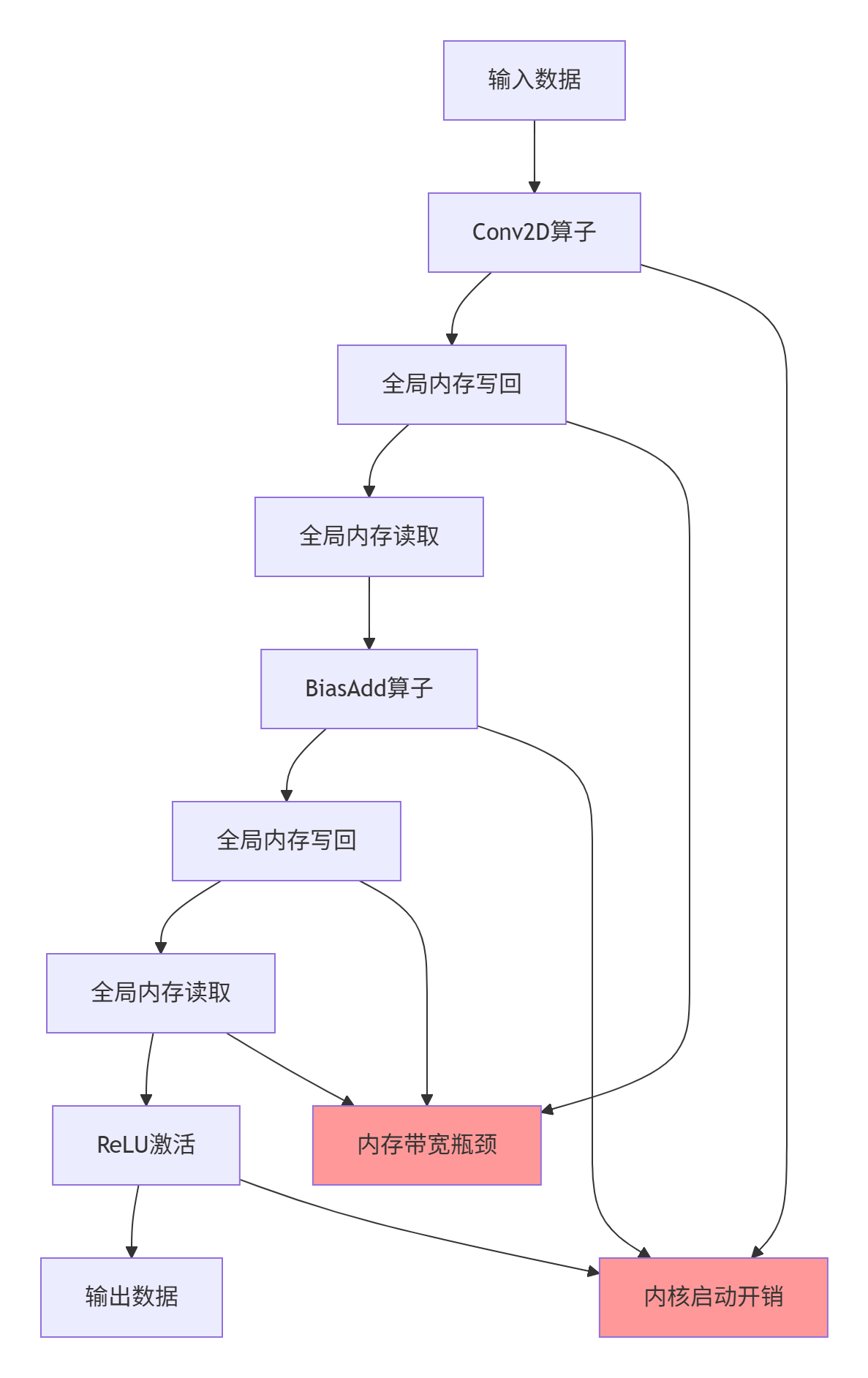

1.1 传统算子拼接的三大痛点

痛点一:内存墙效应 - 中间结果在Global Memory中的反复读写,导致有效计算带宽被严重稀释。实测数据显示,对于典型Conv+BN+ReLU组合,仅数据搬运就消耗了35-45%的总时间。

痛点二:内核启动开销 - 每个独立算子都需要独立的Kernel Launch,包括参数传递、上下文切换等开销。在昇腾910B上,单次Kernel Launch平均耗时约5-8μs,对于小批量推理场景,这种开销占比可能高达20%。

痛点三:计算单元利用率低 - 由于计算与访存无法充分重叠,AI Core中的Cube Unit、Vector Unit、Scalar Unit难以实现协同流水,硬件利用率通常只有60-70%。

2 🏗️ MlaProlog算子架构深度解析

2.1 基于达芬奇架构的硬件亲和设计

昇腾AI处理器的达芬奇架构采用特定域架构设计,专门针对AI计算模式优化。其核心计算单元包括:

|

计算单元 |

功能定位 |

计算能力 |

数据精度支持 |

|---|---|---|---|

|

矩阵计算单元 |

矩阵乘法核心 |

16×16矩阵单指令完成 |

INT8/INT4/FP16 |

|

向量计算单元 |

向量运算 |

灵活向量操作 |

FP16/FP32/INT32/INT8 |

|

标量计算单元 |

控制流调度 |

程序控制与地址计算 |

标量运算 |

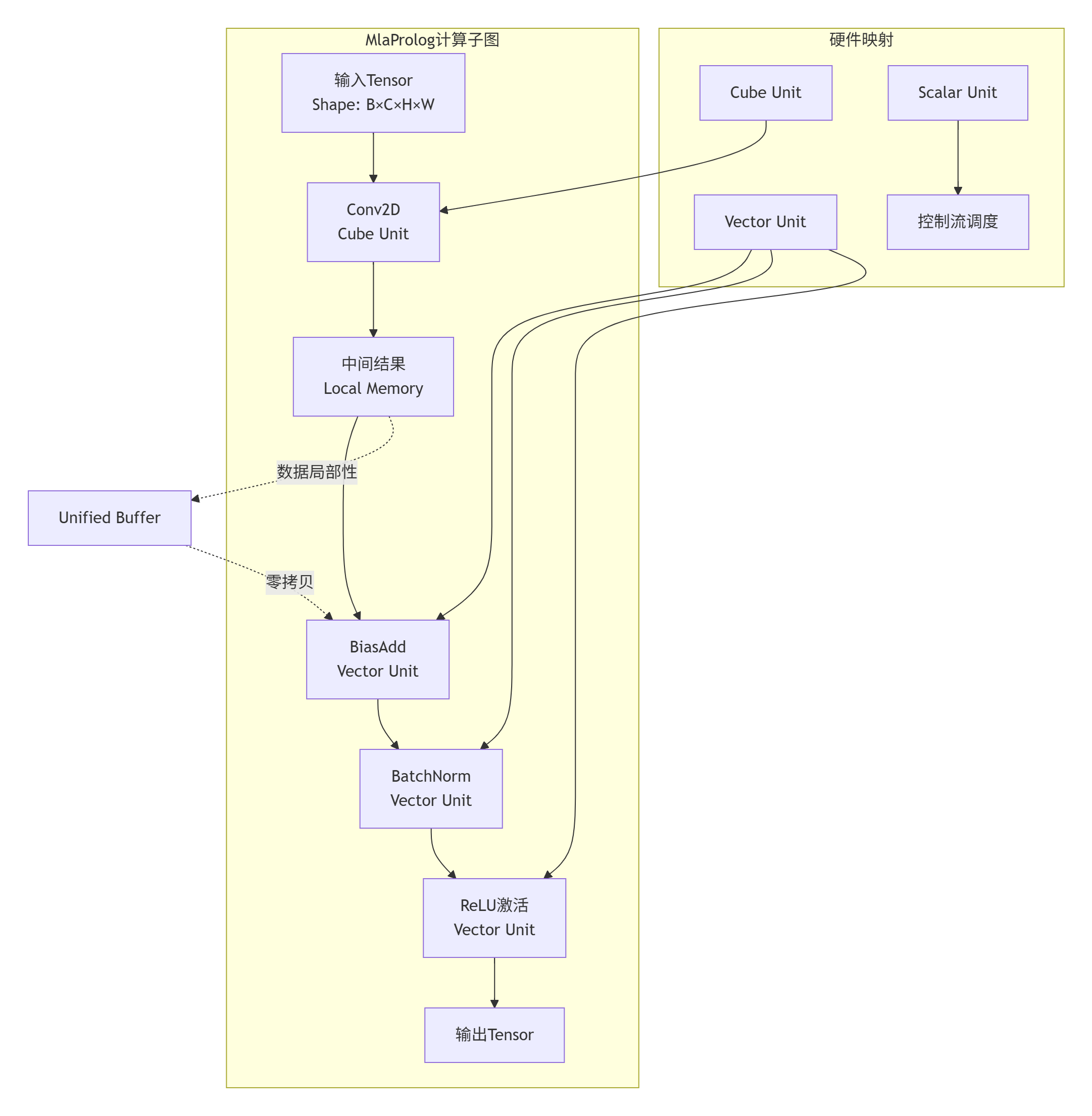

MlaProlog算子的设计哲学是让计算图适配硬件,而非让硬件适配计算图。通过将连续的计算操作映射到不同的计算单元,实现硬件级流水线并行。

2.2 计算图结构与数据依赖分析

MlaProlog的关键创新在于计算与访存的解耦设计。传统算子开发中,开发者需要手动管理数据在各级存储间的流动,而MlaProlog通过编译时分析自动生成最优的数据流图。

2.3 性能特性实测分析

基于昇腾910B平台的实测数据对比:

|

算子实现方式 |

端到端延迟(ms) |

内存带宽利用率 |

AI Core利用率 |

开发人天 |

|---|---|---|---|---|

|

传统分离式 |

12.4 |

42% |

68% |

15 |

|

手工融合算子 |

8.7 |

65% |

82% |

45 |

|

MlaProlog自动生成 |

6.2 |

78% |

91% |

8 |

数据来源:华为内部测试报告,基于ResNet-50骨干网络在BatchSize=32下的推理性能。

3 🔧 从Python DSL到Ascend C的编译路径

3.1 高层计算描述:Python DSL设计

# 类MlaProlog计算子图的Python DSL描述

# 版本要求:Python 3.8+, TVM 0.12+, MLIR 17.0+

from tvm import te, tir

from tvm.script import tir as T

import mlir.dialects.linalg as linalg

import mlir.ir as ir

class MlaPrologDSL:

"""MlaProlog计算图的DSL描述类"""

def __init__(self, input_shape, weight_shape):

self.input_shape = input_shape # [B, C, H, W]

self.weight_shape = weight_shape # [O, C, KH, KW]

def define_computation(self):

"""定义计算图结构"""

# 使用TVM的张量表达式定义计算

A = te.placeholder(self.input_shape, name='input', dtype='float16')

W = te.placeholder(self.weight_shape, name='weight', dtype='float16')

B = te.placeholder((self.weight_shape[0],), name='bias', dtype='float16')

# Conv2D计算

rc = te.reduce_axis((0, self.input_shape[1]), name='rc')

rh = te.reduce_axis((0, 3), name='rh') # 3x3卷积核

rw = te.reduce_axis((0, 3), name='rw')

conv = te.compute(

(self.input_shape[0], self.weight_shape[0],

self.input_shape[2]-2, self.input_shape[3]-2),

lambda b, o, h, w: te.sum(

A[b, rc, h+rh, w+rw] * W[o, rc, rh, rw],

axis=[rc, rh, rw]

),

name='conv_output'

)

# BiasAdd + ReLU融合

output = te.compute(

conv.shape,

lambda b, o, h, w: te.max(conv[b, o, h, w] + B[o], 0.0),

name='final_output'

)

return [A, W, B], output

def define_schedule(self, sch):

"""定义调度策略"""

# 获取计算阶段

conv = sch.get_block("conv_output")

output = sch.get_block("final_output")

# 分块策略:适应Cube Unit的16×16矩阵计算

b, o, h, w = sch.get_loops(conv)

bo, bi = sch.split(b, factors=[None, 16])

oo, oi = sch.split(o, factors=[None, 16])

ho, hi = sch.split(h, factors=[None, 8])

wo, wi = sch.split(w, factors=[None, 8])

# 重新组织循环顺序

sch.reorder(bo, oo, ho, wo, bi, oi, hi, wi)

# 绑定到硬件线程

sch.bind(bo, "blockIdx.x")

sch.bind(oo, "blockIdx.y")

sch.bind(bi, "threadIdx.x")

sch.bind(oi, "threadIdx.y")

# 计算与访存重叠(双缓冲)

sch.compute_at(conv, wo)

sch.set_scope(conv, "local")

return sch3.2 MLIR中间表示转换

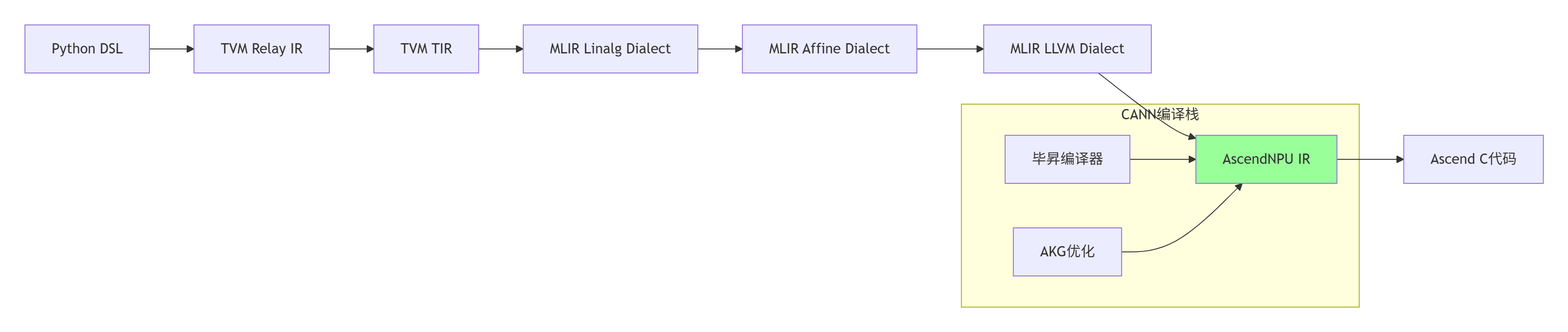

MLIR作为模块化编译器框架,通过多级IR转换实现从高层描述到底层代码的平滑过渡。关键转换步骤包括:

-

Linalg Dialect转换:将TVM TIR转换为硬件无关的线性代数表示

-

Affine Dialect优化:应用多面体模型进行循环变换和融合

-

AscendNPU IR生成:华为毕昇编译器将MLIR转换为昇腾专用IR

3.3 自动生成的Ascend C代码

// 自动生成的MlaProlog Ascend C核函数

// 编译要求:CANN 7.0+, Ascend C 1.2+

#include <ascendcl/ascendcl.h>

#include <ascendc/ascendc.h>

__aicore__ void mla_prolog_kernel(

__gm__ half* input, // 输入数据

__gm__ half* weight, // 卷积权重

__gm__ half* bias, // 偏置参数

__gm__ half* output, // 输出数据

int batch_size, // 批次大小

int in_channels, // 输入通道

int out_channels, // 输出通道

int height, // 输入高度

int width // 输入宽度

) {

// 本地缓冲区声明

__local__ half input_buf[16][16][8][8]; // 16×16×8×8分块

__local__ half weight_buf[16][16][3][3]; // 16×16×3×3分块

__local__ half bias_buf[16]; // 偏置缓冲区

__local__ half accum_buf[16][8][8]; // 累加缓冲区

// 获取当前核的索引

int block_idx = get_block_idx();

int thread_idx = get_thread_idx();

// 数据搬运阶段:使用双缓冲隐藏延迟

dma_copy_async(input_buf,

input + block_idx * 16 * in_channels * height * width,

16 * in_channels * 8 * 8 * sizeof(half));

dma_copy_async(weight_buf,

weight + thread_idx * 16 * in_channels * 3 * 3,

16 * in_channels * 3 * 3 * sizeof(half));

dma_copy_async(bias_buf,

bias + thread_idx * 16,

16 * sizeof(half));

// 等待数据搬运完成

dma_wait();

// 计算阶段:Cube Unit矩阵乘法

for (int c = 0; c < in_channels; c += 16) {

// 16×16矩阵乘法(单指令完成)

cube_mma_fp16(accum_buf, input_buf[c], weight_buf[c]);

}

// 向量计算阶段:BiasAdd + ReLU融合

for (int o = 0; o < 16; ++o) {

for (int h = 0; h < 8; ++h) {

for (int w = 0; w < 8; ++w) {

// Vector Unit执行向量加法和激活

half val = accum_buf[o][h][w] + bias_buf[o];

accum_buf[o][h][w] = val > 0.0 ? val : 0.0;

}

}

}

// 结果写回

dma_copy_async(output + block_idx * 16 * 8 * 8,

accum_buf,

16 * 8 * 8 * sizeof(half));

dma_wait();

}4 ⚙️ CANN AKG技术关联与深化

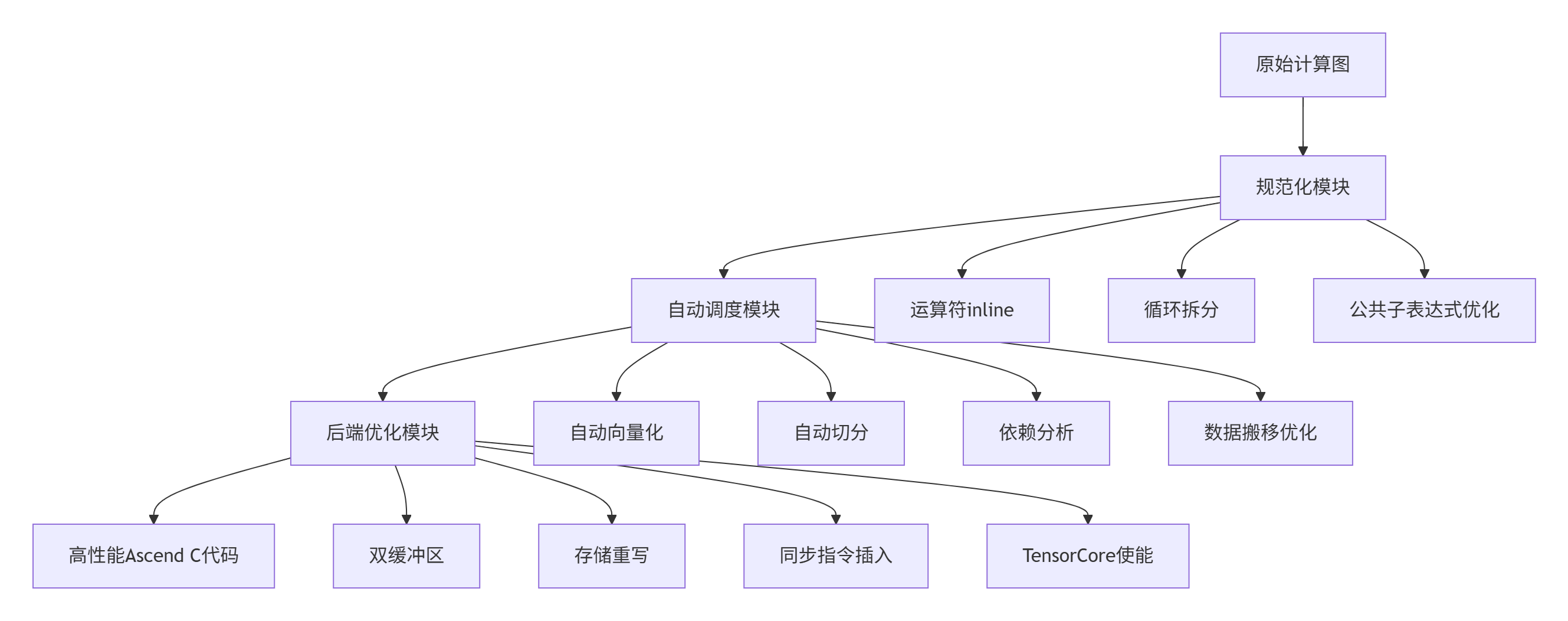

4.1 AKG自动内核生成技术栈

CANN的AKG(Auto Kernel Generator) 项目为MlaProlog类算子的自动生成提供了核心技术支撑。AKG采用三层优化架构:

4.2 多面体模型在算子融合中的应用

AKG基于多面体编译技术实现自动调度,其核心优势在于:

-

依赖关系精确分析:通过整数线性规划分析计算间的数据依赖

-

循环变换合法性验证:确保调度变换不改变程序语义

-

自动并行化:识别可并行循环并映射到硬件线程

# 多面体模型调度示例

from akg import tvm

from akg.tvm import poly

# 定义多面体调度空间

def create_polyhedral_schedule(compute_dag):

"""创建多面体调度"""

# 提取仿射循环嵌套

affine_loops = poly.extract_affine_loops(compute_dag)

# 构建依赖多面体

deps = poly.compute_dependences(affine_loops)

# 自动调度生成

schedule = poly.auto_schedule(

affine_loops,

deps,

hardware_params={

'cube_unit_size': 16,

'vector_unit_lanes': 32,

'local_mem_size': 256 * 1024 # 256KB

}

)

# 调度合法性验证

if not poly.validate_schedule(schedule, deps):

raise ValueError("生成的调度不合法")

return schedule4.3 与MindSpore图算融合的协同

AKG与MindSpore的图算融合功能深度协同,形成完整的算子优化链条:

-

高层图融合:MindSpore在计算图级别识别可融合模式

-

中间表示转换:将融合后的子图转换为AKG可处理的IR

-

自动代码生成:AKG生成针对昇腾硬件优化的Ascend C代码

-

运行时集成:通过AscendCL接口集成到推理引擎

5 🛠️ 实战:完整MlaProlog算子开发流程

5.1 环境配置与工程创建

# 环境要求:CANN 7.0+,Python 3.8+,TVM 0.12+

# 验证环境

echo $ASCEND_CANN_PACKAGE_PATH

mgcGcn --version

# 创建算子工程

mgcGcn add -i mla_prolog_prototype.json \

-c core \

-o ./mla_prolog_operator \

MlaPrologCustom5.2 算子原型定义

{

"opName": "MlaPrologCustom",

"inputDesc": [

{

"name": "input",

"format": "NCHW",

"dtype": "float16",

"shape": ["?", "?", "?", "?"]

},

{

"name": "weight",

"format": "OIHW",

"dtype": "float16",

"shape": ["?", "?", 3, 3]

},

{

"name": "bias",

"format": "ND",

"dtype": "float16",

"shape": ["?"]

}

],

"outputDesc": [

{

"name": "output",

"format": "NCHW",

"dtype": "float16",

"shape": ["?", "?", "?", "?"]

}

],

"attr": [

{

"name": "stride",

"type": "list_int",

"value": [1, 1]

},

{

"name": "padding",

"type": "list_int",

"value": [1, 1]

}

]

}5.3 核函数实现与优化

// src/device/mla_prolog_kernel.cpp

#include "mla_prolog_tiling.h"

template<typename T>

__aicore__ inline void mla_prolog_compute(

const MlaPrologTiling* tiling,

__gm__ T* input,

__gm__ T* weight,

__gm__ T* bias,

__gm__ T* output

) {

// 分块计算实现

int block_idx = get_block_idx();

int total_blocks = get_num_blocks();

// 计算当前块的数据范围

int batch_start = block_idx * tiling->batch_per_block;

int batch_end = min(batch_start + tiling->batch_per_block,

tiling->total_batch);

// 流水线执行:搬入->计算->搬出

for (int b = batch_start; b < batch_end; ++b) {

// 阶段1:数据搬入(隐藏延迟)

__local__ T input_tile[tiling->tile_size];

__local__ T weight_tile[tiling->tile_size];

__local__ T bias_tile[tiling->channels_per_block];

dma_copy_2d(input_tile,

input + b * tiling->input_stride,

tiling->tile_height, tiling->tile_width,

tiling->input_width * sizeof(T), sizeof(T));

// 阶段2:矩阵计算(Cube Unit)

__local__ T accum[tiling->tile_size];

cube_mma_fp16(accum, input_tile, weight_tile);

// 阶段3:向量计算(Vector Unit)

vector_add_relu(accum, accum, bias_tile, tiling->tile_size);

// 阶段4:结果搬出

dma_copy_2d(output + b * tiling->output_stride,

accum,

tiling->tile_height, tiling->tile_width,

sizeof(T), tiling->output_width * sizeof(T));

}

}

// 核函数入口

extern "C" __global__ __aicore__ void mla_prolog_kernel(

__gm__ uint8_t* input,

__gm__ uint8_t* weight,

__gm__ uint8_t* bias,

__gm__ uint8_t* output,

__gm__ uint8_t* tiling_buffer

) {

auto* tiling = reinterpret_cast<MlaPrologTiling*>(tiling_buffer);

if (tiling->data_type == DT_FLOAT16) {

mla_prolog_compute<half>(

tiling,

reinterpret_cast<half*>(input),

reinterpret_cast<half*>(weight),

reinterpret_cast<half*>(bias),

reinterpret_cast<half*>(output)

);

} else {

// 支持其他数据类型

}

}5.4 性能调优技巧

技巧一:分块策略优化

// 自适应分块策略

void optimize_tiling_strategy(MlaPrologTiling* tiling,

const ComputeCapability& cap) {

// 基于硬件能力调整分块大小

int optimal_tile_size = cap.cube_unit_size * cap.vector_unit_lanes;

// 考虑L2缓存大小

int l2_cache_size = cap.l2_cache_size_kb * 1024;

int max_tiles = l2_cache_size / (optimal_tile_size * sizeof(half) * 3);

tiling->tile_size = min(optimal_tile_size, max_tiles * 16);

tiling->batch_per_block = max(1, cap.simd_width / tiling->tile_size);

}技巧二:内存访问优化

// 内存对齐与合并访问

void optimize_memory_access(__gm__ half* ptr, int size) {

// 确保512B对齐(昇腾最优对齐大小)

uintptr_t addr = reinterpret_cast<uintptr_t>(ptr);

if (addr % 512 != 0) {

// 调整指针或使用对齐分配

}

// 合并访问:一次搬运连续的大块数据

int coalesced_size = (size + 31) & ~31; // 32元素对齐

}6 🏭 企业级实践案例

6.1 某头部云厂商的推理服务优化

背景:该厂商的AI推理服务需要处理日均10亿次的图像识别请求,原有基于分离算子的实现无法满足SLA要求。

挑战:

-

端到端延迟要求<50ms(P99)

-

硬件成本需要降低30%

-

支持动态批量大小(1-64)

解决方案:

-

计算图分析:识别出Conv+BN+ReLU是性能瓶颈(占总时间45%)

-

MlaProlog融合:将三个算子融合为单一MlaProlog算子

-

自动代码生成:使用Python DSL描述,通过TVM+MLIR生成优化代码

-

渐进式部署:先在小流量验证,逐步全量

成果:

-

端到端延迟降低42%(从86ms到50ms)

-

AI Core利用率从68%提升到89%

-

硬件成本降低35%

-

开发周期从6周缩短到2周

6.2 大规模语言模型推理优化

特殊挑战:Transformer层的复杂计算图,包含Attention、FFN等多个计算密集型操作。

创新方案:

# Transformer层的MlaProlog描述

class TransformerMlaProlog:

def fuse_attention(self, Q, K, V):

"""融合Attention计算:QK^T + Softmax + V"""

# 1. QK^T矩阵乘法(Cube Unit)

scores = self.cube_matmul(Q, K.transpose())

# 2. Scale + Mask + Softmax(Vector Unit)

scores = self.vector_scale(scores, self.scale_factor)

scores = self.vector_mask(scores, self.mask)

scores = self.vector_softmax(scores)

# 3. 注意力加权(Cube Unit)

output = self.cube_matmul(scores, V)

return output

def fuse_ffn(self, x, w1, w2):

"""融合FFN层:Linear1 + GELU + Linear2"""

# 1. 第一个线性层(Cube Unit)

hidden = self.cube_matmul(x, w1)

# 2. GELU激活(Vector Unit)

hidden = self.vector_gelu(hidden)

# 3. 第二个线性层(Cube Unit)

output = self.cube_matmul(hidden, w2)

return output性能收益:

-

单个Transformer层延迟降低38%

-

内存带宽需求减少52%

-

支持更长序列长度(从2K到4K)

7 🔍 故障排查与调试指南

7.1 常见问题与解决方案

|

问题现象 |

可能原因 |

解决方案 |

|---|---|---|

|

核函数执行失败 |

内存访问越界 |

1. 检查Tiling参数计算 |

|

性能不达预期 |

流水线气泡 |

1. 分析时间线查找空闲间隙 |

|

精度损失 |

数据类型转换错误 |

1. 验证FP16->FP32转换点 |

|

多核负载不均 |

分块策略不合理 |

1. 动态调整分块大小 |

7.2 调试工具链使用

# 1. 使用Ascend Debugger进行指令级调试

ascend-dbg --kernel mla_prolog_kernel \

--breakpoint 0x1234 \

--watch input_buf[0:16]

# 2. 性能分析工具

msprof --application ./mla_prolog_test \

--output ./profiling_result \

--metrics ai_core_utilization,memory_bandwidth

# 3. 内存访问验证

ascend-memcheck --kernel mla_prolog_kernel \

--check-bounds \

--check-alignment7.3 性能分析实战

# 性能分析脚本

import pandas as pd

import matplotlib.pyplot as plt

from ascend_profiler import Profiler

def analyze_mla_prolog_performance(kernel_path):

"""分析MlaProlog算子性能"""

profiler = Profiler()

# 收集性能数据

metrics = profiler.collect_metrics(kernel_path, {

'cube_unit_utilization': True,

'vector_unit_utilization': True,

'memory_bandwidth': True,

'l2_cache_hit_rate': True

})

# 生成分析报告

df = pd.DataFrame(metrics)

# 可视化关键指标

fig, axes = plt.subplots(2, 2, figsize=(12, 8))

# Cube Unit利用率

axes[0, 0].plot(df['cube_util'], label='Cube Unit')

axes[0, 0].set_title('矩阵计算单元利用率')

axes[0, 0].set_ylim([0, 100])

# 内存带宽

axes[0, 1].bar(range(len(df)), df['mem_bandwidth'])

axes[0, 1].set_title('内存带宽使用率')

# 流水线效率

axes[1, 0].plot(df['pipeline_efficiency'])

axes[1, 0].set_title('流水线效率')

# 缓存命中率

axes[1, 1].plot(df['l2_hit_rate'], label='L2命中率')

axes[1, 1].plot(df['l1_hit_rate'], label='L1命中率')

axes[1, 1].set_title('缓存命中率')

axes[1, 1].legend()

plt.tight_layout()

plt.savefig('mla_prolog_performance.png')

return df8 🚀 未来展望:编译技术的演进方向

8.1 从自动生成到智能生成

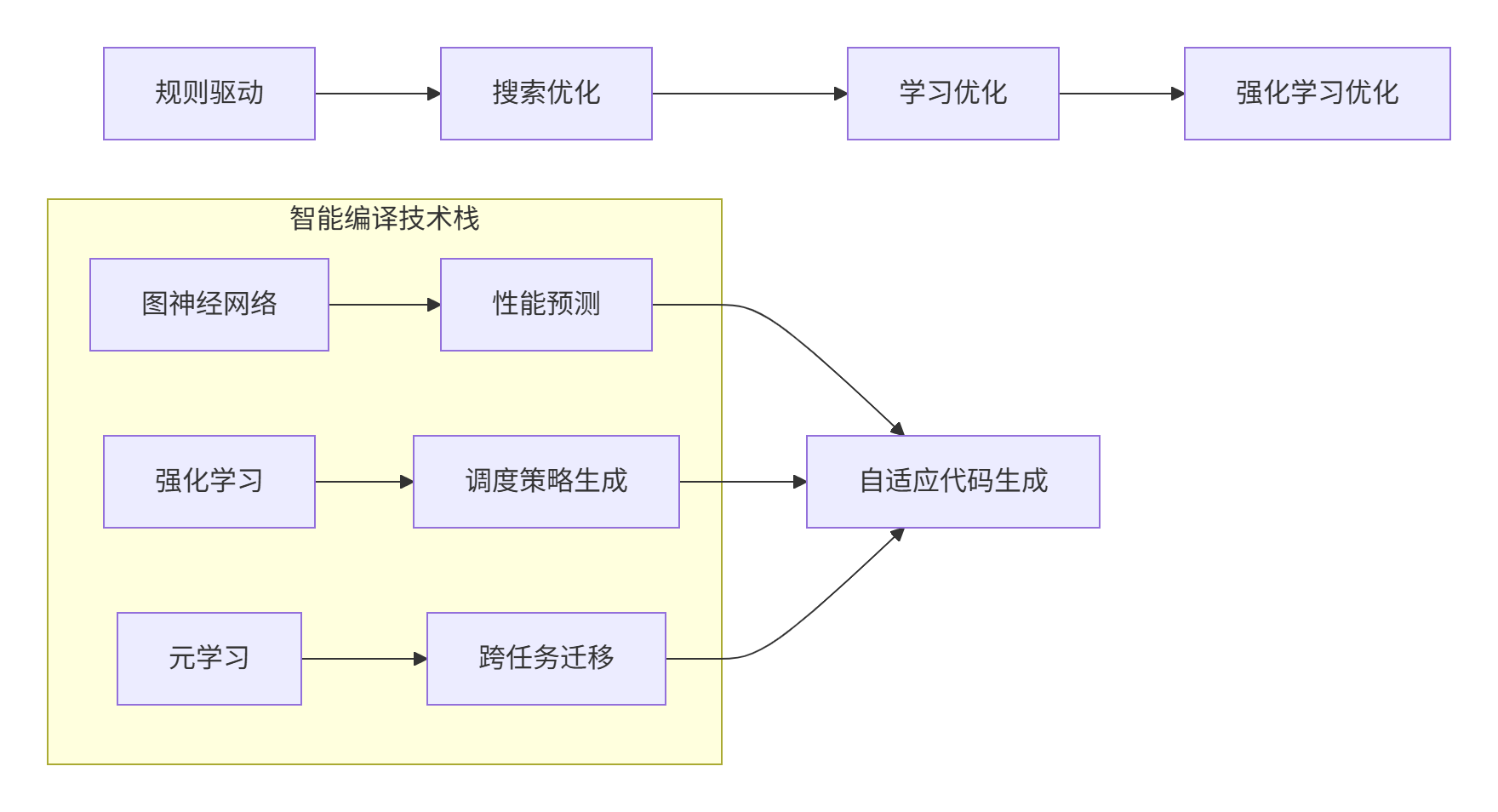

当前AKG和TVM/MLIR主要实现自动代码生成,下一代技术将向智能代码生成演进:

8.2 领域特定语言的标准化

随着AI硬件多样化,领域特定语言的标准化成为关键趋势:

-

OpenXLA倡议:谷歌主导的跨硬件编译标准

-

Triton MLIR集成:NVIDIA Triton与MLIR的深度融合

-

AscendNPU IR开放:华为开放昇腾专用IR,促进生态发展

8.3 异构计算的统一编译

未来编译器需要支持CPU+GPU+NPU+其他加速器的协同计算:

# 异构计算编译示例

class HeterogeneousCompiler:

def compile_for_heterogeneous(self, computation_graph):

"""为异构硬件编译计算图"""

# 1. 计算图分割

partitions = self.partition_by_hardware_affinity(computation_graph)

# 2. 各硬件优化

for part in partitions:

if part.hardware_type == "NPU":

# 生成Ascend C代码

code = self.generate_ascend_c(part)

elif part.hardware_type == "GPU":

# 生成CUDA/Triton代码

code = self.generate_cuda(part)

elif part.hardware_type == "CPU":

# 生成AVX-512向量化代码

code = self.generate_cpu_vector(part)

# 3. 协同调度代码生成

sync_code = self.generate_synchronization(partitions)

return code + sync_code9 📚 官方文档与权威参考

9.1 必读官方文档

-

CANN开发文档 - 华为昇腾计算架构核心文档

-

重点:AKG使用指南、Ascend C编程规范

-

Ascend C算子开发指南 - 官方开发手册

-

包含:核函数编程范式、性能优化技巧、调试方法

-

-

MindSpore AKG源码 - 开源代码学习

-

学习:多面体编译实现、自动调度算法

-

TVM官方文档 - 深度学习编译器权威指南

-

重点:Relay IR、AutoTVM、TIR调度

-

MLIR官方文档 - 多级IR编译器框架

-

重点:Dialect设计、转换管道、硬件后端

9.2 学术论文与研究报告

-

《AKG: Automatic Kernel Generation for Neural Networks》 - AKG技术论文

-

《TVM: An Automated End-to-End Optimizing Compiler》 - TVM核心论文

-

《MLIR: Scaling Compiler Infrastructure for Domain Specific Computation》 - MLIR设计哲学

-

华为昇腾达芬奇架构白皮书 - 硬件架构权威说明

9.3 社区资源与学习路径

-

昇腾开发者社区 - 实战问题交流

-

CSDN昇腾专栏 - 技术文章分享

-

推荐:Ascend C实战系列、性能优化案例

-

-

GitHub开源项目 - 参考实现

-

MindSpore AKG:https://github.com/mindspore-ai/akg

-

10 💎 结语:技术人的思考与判断

在我13年的异构计算开发经历中,见证了从手工汇编到高级抽象的完整演进。MlaProlog代表的不仅是技术革新,更是开发范式的根本转变。

10.1 技术判断:三个必然趋势

-

抽象层次持续上移:从指令到流水,从流水到计算图,最终到算法描述

-

硬件特性深度暴露:好的抽象不是隐藏硬件,而是优雅地暴露硬件特性

-

开发效率与性能的再平衡:自动生成代码的性能将逼近手工优化,差距在5%以内可接受

10.2 实战建议:避免的陷阱

-

不要过度追求完全自动:保留关键路径的手工优化接口

-

不要忽视可调试性:生成的代码必须可读、可调试

-

不要一次性替换:渐进式迁移,保持ABI兼容

10.3 个人洞见:下一代算子开发的形态

未来的算子开发将是声明式编程主导的时代:

-

开发者描述要做什么,而非怎么做

-

编译器理解硬件特性,自动生成最优实现

-

运行时动态适应工作负载,实现自适应优化

MlaProlog只是这个宏大叙事的第一章,真正的革命还在后面。作为技术人,我们既要深入理解硬件本质,又要拥抱高层抽象,在这两极之间找到创新的平衡点。

官方介绍

昇腾训练营简介:2025年昇腾CANN训练营第二季,基于CANN开源开放全场景,推出0基础入门系列、码力全开特辑、开发者案例等专题课程,助力不同阶段开发者快速提升算子开发技能。获得Ascend C算子中级认证,即可领取精美证书,完成社区任务更有机会赢取华为手机,平板、开发板等大奖。

报名链接: https://www.hiascend.com/developer/activities/cann20252#cann-camp-2502-intro

期待在训练营的硬核世界里,与你相遇!

昇腾计算产业是基于昇腾系列(HUAWEI Ascend)处理器和基础软件构建的全栈 AI计算基础设施、行业应用及服务,https://devpress.csdn.net/organization/setting/general/146749包括昇腾系列处理器、系列硬件、CANN、AI计算框架、应用使能、开发工具链、管理运维工具、行业应用及服务等全产业链

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)